(Samsung Foundry Forum)

(Samsung Foundry Forum)

在2018年5月22日在美國加州Santa Clara舉辦的Samsung Foundry Forum中,

三星針對他們半導體製造的最新進度與計畫做了一系列的介紹與進度說明,

包括他們即將在2019量產、採用EUV的7nm Low Power Plus (7LPP),還有他們在先進封裝、FDSOI、EUV量產化等技術上的努力,

不過最受矚目的,就是他們正式發布他們在5奈米製程之後的規劃,包括5、4、3奈米共三個製程節點,

其中,5、4奈米都是使用FinFET架構,包括5nm Low Power Early (5LPE)、4nm Low Power Early (4LPE)、4nm Low Power Plus (4LPP),

而從3奈米開始,他們將走向新的架構: 3nm Gate All Around Early (3GAAE),甚至從2019年起就提供初步的製程設計套件 (PDK),

這是目前業界已公開最積極的技術發展路線藍圖,足見三星電子在半導體製程發展上的野心。

傳統上的MOSFET是採用「平面式結構」,其閘極電壓 (gate voltage)的電場能有效調控與通道靠近閘氧化層區域的電位,

然而隨著製程不斷微縮,

不斷縮小的閘極長度造成的「短通道效應」將讓此一傳統結構難以阻絕源極 (source)與汲極 (drain)之間的漏電流,

隨著平面式結構的製程微縮陷入困境,Intel在22奈米,三星/台積電則是在14/16奈米製程世代開始採用立體結構,

也就是所謂 "FinFET"「鰭式場效電晶體」,此一結構的通道是豎起來而被閘極給包圍起來的,因長得像魚鰭而得其名,

如此一來閘極偏壓便能有效調控通道電位,因而改良開關特性,

但是FinFET在經歷14/16、7/10這兩個製程世代後,不斷拉高的深寬比 (aspect ratio)讓前段製程已逼近物理極限,

在繼續微縮的話,先不提電性是否還能有效提升,就結構而言就已有許多問題,

比方說以矽形成的「鰭」由於材料內部應力作用,太細、高的「鰭」會無法維持直立的形狀而形成「扭線」 (wiggling),

而在極紫外光 (EUV)導入製程後,此一狀況會更嚴重,原因是光子本身存在的隨機效應造成photon shot noise現象,

更何況,不斷微縮後,越來越細的閘極對通道的控制能力不足,鰭狀通道底部終究還是會成為漏電流的來源,

因此學術界很早開始就提出5奈米以下的製程需要走 "Gate All Around"(GAA),中文稱為「環繞式閘極」的結構,

顧名思義,

是FinFET中已經被閘極給三面環繞的通道,在GAA中將是被閘極給四面包圍,預期此一結構將達到更好的供電與開關特性,

只要靜電控制能力增加,則閘極的長度微縮就能持續進行,摩爾定律重新獲得延續的動力。

(IMEC)

(IMEC)

要達到環繞式閘極的結構,最常見的是將通道做成 "奈米線" (nanowire)或"奈米片" (nanosheet)的形狀,

下面所示的便是比利時微電子研究中心 (IMEC)在2016年發表的奈米線結構。

三星很早就開始研究GAA架構,並和IBM與Global Foundries合作,在2017年便在VLSI超大型積體電路專論會中發表相關文獻,

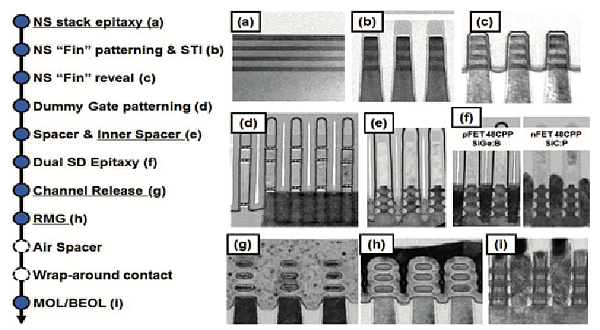

他們製造出來的環繞式閘極結構如下圖所示,代號叫MBCFET 多橋通道FET,係以奈米片堆疊而成,

他們同時公布了大略的製程流程圖,

可以注意到許多與現在FinFET不同之處,包括一開始需要以Epi的方式將矽層 (Si) 與矽鍺層 (SiGe)進行堆疊 (NS stack epitaxy),

SiGe是做為「犧牲層」(sacrificial SiGe),

在之後要進行所謂 "channel release"即步驟g,

利用高選擇比的蝕刻把SiGe吃光來獲得奈米線或奈米片,如此一來就會形成一層一層的奈米片(線)。

很多人會好奇,為何奈米線能這樣維持在空中呢? 原因是有dummy gate在支撐著,就好像橋墩支撐著橋樑一樣。

另外,在(e)步驟提到 "inner spacer",

它除了能夠在channel release製程時把 SD epitaxy的材料和用來蝕刻channel的氣體給隔絕開以外,

也能大幅降低元件的寄生電容,是GAA的一大重點要角。 (IEEE Transactions on Electron Devices ( Volume: 64, Issue: 12, Dec. 2017) )。

(此為Applied Materials 與IMEC合作的inner spacer 版本,可以注意到在inner spacer 以ALD的方式疊上去後,epi長在外面,

所謂 dummy gate 則會在RMG 被移除填入HKMG,inner spacer 正是在此時達到隔絕的效果)

根據報告,三星/IBM/Global Foundries已經找到辦法製作出均勻度 (uniformity)、穩定性均佳的環繞式閘極結構,

比方說,由於奈米片在channel release後是懸浮狀態,只是靠著閘極在支撐 (就有如橋梁的道路和橋墩),

如果在設計上沒有最佳化,比方說長度太長,或是製程設計不佳,奈米片之間可能會接合在一起 (stiction),

不過他們已經找到辦法去避免此一情況。

另外,透過將P-metal置換成N-metal,能在元件中創造多個臨界電壓 (threshold voltage),他們同樣也已找到辦法,

利用H2O2,能夠將P-metal給移除,同時不會傷害到奈米片的結構。

最後,他們不但能夠在通道間距 (pitch)放寬的情況下達到和未放寬前一樣的通道寬度 (Weff),

甚至於在最佳化後,發現如果使用更寬的nanosheet,在通道寬度上可以達到30%的提升。

雖然原本預期從5奈米節點開始就能進入GAA世代,

然而GAA的製作難度比FinFET來得更高,加上GAA本身也有其它問題,讓製程也更加複雜,研發成本將大為增加,

在製程方面,為了讓通道成為一條條的奈米線,需要以具有等向性與高選擇比的化學性蝕刻才能達到,

不過為了達到矽層與矽鍺層的高選擇比,除了蝕刻氣體的選擇以外,通常需採低溫製程,代價就是產能會大大降低,

而且,蝕刻的能力會隨著深度遞減,而在現行高深寬比的結構下,結構的均一性 (uniformity)會難以達到需要的水平。

另外,在這種3D結構下,在疊low K 薄膜和金屬閘極時,如何能夠讓這些材料完美包覆奈米線/奈米片,

同時還要能應付5奈米甚至3奈米以下的微縮需求 (pitch越小,能疊的空間越小), 都非常具挑戰性,考驗製程整合和調整的功力。

以三星在年度代工技術論壇上公佈的時程來看,他們已經把GAA的導入時間從最早的5nm世代後退到3nm世代,

至於另外兩家半導體製造巨擘: 英特爾與台積電,

雖然各自都曾表達過對於nanowire、nanosheet等新架構,和鍺、二氧化鉬 (MoS2)等新材料的興趣,

但都不像三星這般公開發表他們在這方面的技術路線與引入時間,這將是值得持續觀察的地方。

(註: 最新進度如下,英特爾宣稱其10奈米製程將再度延後到2019年才開始量產,然而根據公開的技術資料,

包括間距、cell大小等等,英特爾的10奈米製程其實相當於三星、台積電等公司的7奈米製程,

台積電則在2018年的技術研討會上宣布將在2019年初開始5奈米製程的風險性試產,不過未公布技術細節)

業界會對GAA架構抱持保守態度並不讓人意外,

原因是GAA到底是不是延續摩爾定律的最佳解方,其實有待商榷,需要更多驗證,

雖然Gate-All-Around,尤其奈米線 (nanowire FET)擁有比FinFET更好的短通道控制能力,但驅動電流和寄生電容都是問題,

一個簡單的解方就是改變通道形狀以加大驅動電流,三星所提出的奈米片便是其中之一,它比奈米線還來得更厚、寬,

事實上,先前製作圓形nanowire的IMEC在更近期發表的論文中,透過TCAD模擬,

同樣得到將形狀從圓形改成長方形能夠改善電流驅動力 (drivability),for p/nFET 各有13%/18%更高的on current,

原因是量子效應帶來的「鰭體內反轉」(volume inversion)和subband occupation。

除了採用不同形狀的GAA架構以外,還可以透過堆疊的方式,將奈米線或奈米片層層堆疊,

但是如果堆疊得越高,製程的控制上就有更多難以解決的問題 (比方說,蝕刻的離子難以抵達結構深處),增加開發成本。

事實上,這一類的形狀有五花八變,以下是應用材料公司 (applied materials)的資料,顯示了諸如奈米環、六角奈米線等,

這些努力是冀求除了驅動電流以外,也能達到寄生電容的最佳化,

然而,INTEL的資深院士 Mark Bohr認為,他不覺得奈米片是什麼多具變革性的設計,它頂多是橫向擺置的FinFET。

環繞式閘極以外,5奈米以下的電晶體其實還有許多其它選項,

其中一個選項便是在通道中使用載子遷移率比矽還要高的材料,例如矽鍺或是III-V族材料,

或是其它不同的元件設計概念,

包括負電容場效電晶體 (Negative Capacitance FET, NCFET),這是利用在閘極中使用鐵電性材料 (ferroelectric material),

它與目前High-K metal gate中的主材料: 二氧化鉿 (Hafnium dioxide)的作用,會放大電壓,因此突破次臨界斜率的限制,

形成新的陡峭次臨界斜率元件。

NCFET的一個最大優點,就是它不需要大幅改變現有的元件架構,不管是平面式還是鰭式場效電晶體,都可以直接引用此概念。

( Peter Grünberg Institute for Semiconductor Nanolelectronics )

但無論如何,不管是採用環繞式閘極場效電晶體、負電容場效電晶體,或是運用新的材料,在製程整合上都有其挑戰,

對於業界而言,一個能在成本和效能上達到平衡的產品才是有價值的,而沒有一個本文提到的技術是成熟到讓人信服的地步,

因此即便三星已經大張旗鼓地宣布他們在Gate-All-Around的佈局,

但是對台積電、INTEL,甚至Global Foundries與三星自己而言,5nm以下的電晶體發展會走到哪裡,還不能妄下結論。

(Applied Materials)

(Applied Materials)

參考文獻:

https://technews.tw/2015/09/15/what-is-finfet/

Loubet, N., et al. "Stacked nanosheet gate-all-around transistor to enable scaling beyond FinFET." VLSI Technology, 2017 Symposium on. IEEE, 2017.

Mertens, H., et al. "Vertically stacked gate-all-around Si nanowire transistors: Key Process Optimizations and Ring Oscillator Demonstration." Electron Devices Meeting (IEDM), 2017 IEEE International. IEEE, 2017.

Barraud, S., et al. "Vertically stacked-NanoWires MOSFETs in a replacement metal gate process with Electron Devices Meeting (IEDM), 2016 IEEE International. IEEE, 2016.

inner spacer and SiGe source/drain."

Mertens, Hans, et al. "Vertically stacked gate-all-around Si nanowire CMOS transistors with dual work function metal gates." Electron Devices Meeting (IEDM), 2016 IEEE International. IEEE, 2016.

IEEE Transactions on Electron Devices ( Volume: 64, Issue: 12, Dec. 2017)

留言列表

留言列表