曾經,半導體製程經歷過主要透過黃光 (lithography) 縮小間距就能微縮、加強元件效能、降低成本的美好年代,

不過隨後微縮的尺寸越來越接近黃光的極限,需要引入「多重曝光」(multi-patterning),

光罩數目的增加和整合難度的增加,讓黃光微縮帶來的成本和效能紅利已經越來越不足以支持摩爾定律的延續,

因此半導體製程開始走向 "Design technology co-optimization (DTCO)" 以降低對黃光微縮的依賴,

比方說「自我對準」 (self-aligned) 設計、SiGe 通道 (SiGe channel)、空氣間隔層 (airgap spacer)等等,

但是如今製程世代已經一路發展到7奈米 (量產),甚至是5奈米、3奈米,再怎麼微縮也無法突破物理極限,DTCO也已招式出盡,

所以接下來就進入 "System technology co-optimization (STCO) 的年代",

其中一個方向便是近來非常熱門的 "heterogeneous integration" 「異質整合」方案,也就是最近產業新聞上常聽到的2.5D/3D-IC。

會有這個方案是因為在一個晶片中,除了常聽到的SRAM、CPU、GPU以外,還有 Analog、IO等區域,

而在28奈米節點之後,Analog 和 IO 這兩種電路由於本身線路的複雜性,已經不適合再繼續微縮,

於是將這種複雜的電路分出去,再利用「中介層」 (interposer) 將兩個部分給連接在一起和後續封裝,

如此一來 SRAM、CPU、GPU等就能得到更多的微縮空間,同時線路的長度也能縮短。

這時問題就來了: 我們既然能夠將晶片中不同功能的區塊用3D-IC的方式來整合,

那如果半導體的結構也能用3D的方式堆疊 (相對於FinFET和GAAFET等的2D而言),不也是有助於晶片大小的微縮?

在今年 (2018)的VLSI 超大型積體電路會議中,比利時微電子研究中心 (IMEC)就發表了一個具有潛力的新架構,

他們稱之為 "Complementary Field Effect Transistor",簡稱 CFET,

他們預期這個架構可以應用在IMEC自己的3奈米元件 iN3上面,對應到台積電等foundry的節點則是2奈米。

在傳統的互補式金氧半導體 (CMOS)中,PMOS和NMOS是分別位於基板上的兩個平行區塊,

這樣子的 pull-up與 pull-down network (拉上/拉下網路) 是由同一個閘極來控制,

不過在CFET,NFET是被堆疊在PFET的上面,如此一來 standard cell 和 SRAM的面績可以節省達50%,

這樣的架構可以直接套用在FinFET和GAAFET上,甚至可以設計上Fin on GAA, Fin on Fin, 或是GAA on GAA等等。

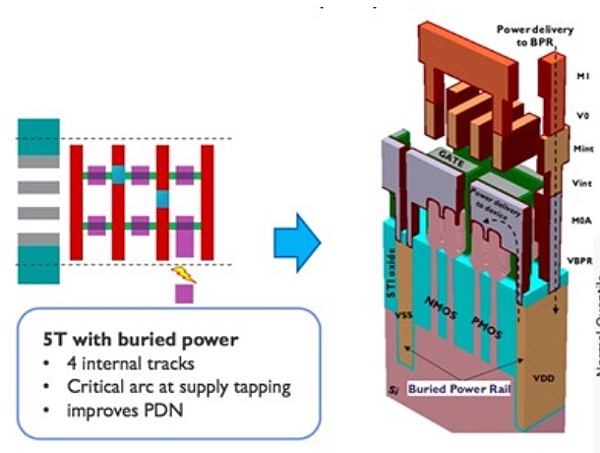

在IMEC提出的CFET架構中,前提是必須使用 "buried power rail (BPR)" 技術,如下圖所示。

他們預期在結合CFET 與 BPR,現行最先進的6 track FinFET libraries 一口氣降到 3 track。

在傳統的MOSFET中,power rail 身為interconnection layer 會犧牲掉 metal pitch 微縮的空間,

同時為了要把高高在上的power rail 和元件給連結起來,需用到大量的internection,因而佔用大量空間,增加cell中track的數目,

於是 IMEC提出BPR技術,善用鰭與鰭之間的空間,將 power rail 「埋設」在元件的深處,

如此一來將 power rail 移到前段製程 (FEOL)中,減少 interconnection 佔用的空間,至少可以減少 1~1.5個 track 的數目,

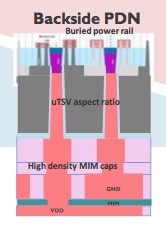

甚至於,既然power rail 已經來到非常接近基板的位置,

那把晶圓給磨薄後,將power grid放在晶圓的背面,從晶背打TSV孔後連接power rail,似乎也成為可能,

在引入BPR後,IMEC 借用了目前FinFET和GAAFET的製作流程,完成了CFET的製程示意圖,

在完成fin和gate 的patterning之後,必須先上一層spacer,接著要去掉fin周圍的spacer,確保能生成P區的epi,

接下來填入底下的金屬電極後,再繼續進行上半部N區的epi和填入金屬,如此一來就基本上完成了CFET的前段製程。

透過下圖便可以看到結合了buried power rail的CFET立體結構示意圖,

傳統上為了要達到cell 內部的繞線 (routing),需要設計兩個正交層,不過在CFET中繞線是在垂直方向進行,

因此可以和中段製程 (middle-end of line, MEOL) 結合在一起,這是CFET之所以能夠大幅降低元件面積的關鍵。

值得注意的是形成這樣的立體結構後,

由於aspect ratio 的增加,要把底層的元件連接到MEOL的繞線需要有很深的VIA (vertical interconnect access)孔,

所以傳統上interconnection 是使用鎢 (tungsten),但在這個新架構中可能要使用釕 (ruthenium),以降低元件的阻值,

但是這又衍生了更多問題,

其中一個問題就是傳統來說,產業界的前段製程 (FEOL) 是不允許金屬的存在,但是如果要採用BPR,就要打破這個原則,

另外,在前段製程中包含了非常多的高溫製程,但是ruthenium對抗這些高溫製程的能力並沒有tungsten這麼好,

而就CFET架構而言,最明顯的挑戰就是堆疊起來的P與N要如何控制 epi的成長與下層金屬的高度,

此外,pFET被埋在下面,會不會讓熱量很難散失,造成散熱設計上的麻煩? 這些都還需要更多數據來驗證,

半導體元件設計與製造是非常資金密集、技術密集與嚴謹的行業,整條產線包含了數千道的程序,一個小誤差會不斷被放大,

任何一點小變動必需要經過非常縝密的評估,才會被納入量產線,

不然以市場「贏家全拿」的特性,

只要下了一個錯誤的決定,就算只是拖延了幾個月的研發時程,也有可能就此底定一個技術節點 (technology node)的 成敗,

甚至於影響公司的命運,

Global Foundries 在 7nm 製程上的敗仗殷鑑不遠,聯電與台積電之間的獲利和股價越差越遠也不是新聞了,

因此,雖然學術界不斷提出新的結構設計與材料,但是真的被台積電、三星等公司納入量產的真的是少之又少,

Complementary FET 的立體電晶體架構是非常新穎的概念,同時還存在有很多疑慮,

但是毫無疑問,Complementary FET的概念能夠有效縮減元件的面積,同時也能馬上容入現行的FinFET或GAAFET,

因此或許我們可以期待數年後,我們能看到CFET正式量產…只要晶圓廠不因為前瞻節點的極高成本與有限市場而決定停止研發。

文獻引用:

Kim, Ryoung-Han, et al. "IMEC N7, N5 and beyond: DTCO, STCO and EUV insertion strategy to maintain affordable scaling trend." Design-Process-Technology Co-optimization for Manufacturability XII. Vol. 10588. International Society for Optics and Photonics, 2018.

The Complementary FET for scaling beyond N3 (2018 VLSI)

留言列表

留言列表